Beyond a Thin Line: How Trace Width Dictates Current Capacity and Thermal Reliability in PCBs

1. Understanding Trace Width: Foundational Concepts in PCB Design

1.1 What is Trace Width: Formal Definition

Trace width refers to the measured horizontal size of a conductive copper path on a printed circuit board. It is typically expressed in millimeters (mm) or mils (thousandths of an inch). Traces form the network of conductors that route electrical signals and supply power across the PCB surface and through its layers.

More formally, trace width, combined with copper thickness, determines the cross-sectional area of the conductor. This cross-sectional area defines the allowable current-carrying capability of the path. The trace width is therefore not simply a routing parameter chosen for convenience; it is an electrical, thermal, and structural constraint specifying how reliably the trace will operate within its intended environment.

To illustrate the physical dimension:

-

A typical digital signal routing trace might be 4–10 mils wide

-

A power distribution trace may require 40–250 mils or more, depending on the current load

-

For inner layers, the copper thickness is thinner, requiring width adjustments to maintain performance equivalence

Trace width also interacts with the laminate and copper surface finish, which affects not only electrical resistance but also signal rise-time behavior and thermal dissipation.

1.2 Electrical Conductivity Principles and Material Influence

The conductive characteristics of a trace depend on copper resistivity, which at room temperature is approximately 1.68 × 10⁻⁸ Ω·m. As the cross-sectional area decreases, electrical resistance increases, generating more heat through Joule heating (I²R loss).

Key variables influencing trace performance include:

| Variable | Influence |

|---|---|

| Copper thickness | Determines cross-sectional area and resistance |

| Trace width | Controls current capacity and thermal distribution |

| PCB substrate thermal conductivity | Dictates heat dissipation efficiency |

| Ambient operating temperature | Affects copper resistivity and expansion |

| Current load profile | Steady vs. pulsed current behaviors differ |

Therefore, a narrower trace may function adequately for high-frequency low-current signals, but would be unsuitable for supplying power or carrying heavy load currents due to excessive self-heating.

1.3 How PCB Copper Thickness Interacts with Trace Width

Copper thickness is defined in ounces per square foot (oz/ft²). Common industry thickness values include:

| Copper Weight | Thickness (μm) | Typical Use Case |

|---|---|---|

| 0.5 oz | 17 µm | Fine signal routing, HDI boards |

| 1.0 oz | 35 µm | Standard board designs |

| 2.0 oz | 70 µm | Higher current or rugged applications |

| 3.0–10 oz | 105–350+ µm | Heavy power distribution, industrial, automotive |

When copper thickness increases, trace width may be reduced for the same current capacity. Conversely, thin copper requires trace width expansion to compensate.

This interplay makes trace width calculation a system-level decision instead of a purely geometrical choice.

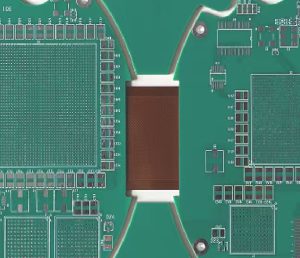

Trace width

2. The Critical Role of Trace Width in PCB Current-Carrying Capability

The ability of a printed circuit board to reliably deliver current across its conductive pathways is central to system stability, operational efficiency, and long-term durability. In power distribution networks, motor drivers, automotive control units, and industrial control boards, the dimension of the conductor directly determines how much current can be carried without excessive thermal rise. The width of the conductive path is therefore one of the primary variables engineers must set based on electrical load requirements rather than simply space constraints.

2.1 The Relationship Between Cross-Sectional Area and Current Density

Risk Indicators When Current Density Exceeds Safe Limits

| Symptom | Cause | System Impact |

|---|---|---|

| Localized thermal hotspots | I²R heating concentration | Component drift, signal instability |

| Darkened resin or board discoloration | Substrate thermal stress | Reduced board lifetime |

| Intermittent power failures | Micro-cracking in copper | System shutdown or erratic operation |

| Catastrophic trace burnout | Sustained overload current | Permanent board failure |

These failure modes are not gradual in all cases. Under repeated current surges or startup inrush conditions, a trace may fail suddenly even if operating smoothly under steady-state current.

Therefore, trace geometry must be calculated based on peak current, continuous average current, and thermal environment, not only the nominal operational current rating.

2.2 Estimating Allowable Current Using Trace Width Calculation Models

Engineers historically relied on empirical charts derived from field failures and thermal laboratory testing to determine appropriate conductor dimensions. One of the most referenced sources for many years was the original IPC-2221 trace width charts. However, these charts assumed natural convection cooling and unsealed laboratory conditions, which differ substantially from real designs.

Modern Standard: IPC-2152

The release of IPC-2152 incorporated updated thermal testing, environmental modeling, and simulation-based current behavior analysis. IPC-2152 demonstrates that heat dissipation is more strongly affected by the PCB’s surrounding thermal environment than previously assumed. Key influencing factors include:

-

Adjacent plane layers acting as heat sinks

-

Board thickness and dielectric thermal conductivity

-

Proximity of high-power components

-

Ambient airflow or forced cooling

-

Whether the trace is external or embedded in inner layers

External traces dissipate heat more efficiently because they radiate directly into surrounding air and benefit from copper surface convection.

Inner layer traces are sandwiched between dielectric layers and lock heat in place, requiring significantly greater conductor area to safely support the same current.

General Observations from IPC-2152

| Trace Location | Implication | Design Requirement |

|---|---|---|

| External copper routing | Better thermal release | Can carry more current for a given width |

| Internal copper routing | Restricted thermal dissipation | Must be wider or use thicker copper |

| Multi-layer boards with ground planes | Heat spreads more effectively | Allows optimized top-layer routing |

| Boards in enclosed environments | Limited convection | Requires conservative current capacity design |

Designers must therefore use IPC-2152 not as a fixed-rule calculator but as a dynamic thermal modeling framework integrated with layout placement strategies.

2.3 IPC-2152 and the Evolution of Trace Width Design Standards

The move from IPC-2221 to IPC-2152 reflects a larger shift in the PCB design industry: performance constraints are no longer assumed to be uniform across all board types. Instead, the effective thermal environment defines how wide a conductor must be in order to maintain operational safety margins.

Thermal Rise and System Reliability

A typical design rule in power electronics is to limit temperature rise to 10–20°C above ambient. Exceeding this range accelerates degradation through:

-

Fracture propagation within copper grain boundaries

-

Softening and reflow of bonding resin

-

Time-dependent dielectric breakdown (TDDB)

-

Long-term expansion/contraction cycle stress

Therefore, the conductor width must be sized not merely to prevent failure, but to slow degradation rates over the product’s intended lifespan.

3. Thermal Reliability and Heat Dissipation Influenced by Trace Width

Electrical current traveling through copper conductors generates heat due to resistive loss, and this heat must be effectively managed to ensure long-term PCB reliability. When the conductor dimension is insufficient, localized temperature rise can propagate through the substrate and adjacent components, accelerating material degradation processes. Understanding how conductor geometry influences thermal behavior is therefore essential for both performance and product durability.

3.1 Joule Heating and Temperature Rise Mechanisms

Factors Affecting Heat Accumulation

| Factor | Effect on Temperature Rise | Notes |

|---|---|---|

| Conductor width | Narrower conductors lead to higher resistance | Increases surface temperature |

| Copper thickness | Thicker copper improves conduction efficiency | Reduces I²R loss per unit length |

| Board layer location | Inner-layer conductors trap heat | External layers allow airflow cooling |

| Substrate material | Thermal conductivity influences heat dissipation path | FR-4 dissipates heat less efficiently than ceramics |

| Ambient temperature | Higher environment temperature reduces cooling rate | Exacerbates thermal stress |

As heat accumulates in the conductor, it spreads through the laminate and surrounding copper structures. If thermal equilibrium cannot be reached, a sustained temperature rise leads to structural and reliability concerns.

Thermal Degradation Behaviors

-

Resin near overheated conductors can brown, soften, or carbonize

-

Repeated thermal cycling can create mechanical fatigue in the copper grains

-

High temperatures accelerate oxidation, reducing electrical conductivity further

-

Excessive heating can trigger delamination, separating copper and substrate layers

As a result, thermal failures are often progressive, developing gradually before cascading into critical system malfunction.

3.2 Copper Expansion, Stress Accumulation, and Long-Term Reliability

Copper expands when heated. When a conductor operates under fluctuating load conditions, it undergoes repetitive expansion and contraction cycles, generating mechanical stress in both the copper and surrounding substrate. Over time, this mechanical cycling can initiate micro-fractures in the conductor or weaken the copper-substrate bond interface.

Thermal Expansion Coefficients and Mechanical Mismatch

| Material | Coefficient of Thermal Expansion (CTE) |

|---|---|

| Copper | ~16–17 ppm/°C |

| Standard FR-4 Laminate | ~14–70 ppm/°C (depending on direction) |

The mismatch between copper and dielectric expansion behavior means that trace geometry plays a direct role in how much stress is generated. Wider conductors distribute expansion forces across a greater surface area, reducing the strain at the interface. Narrow conductors, by contrast, concentrate stress more sharply, increasing the likelihood of crack initiation.

Failure Modes Resulting from Thermal Cycling

| Failure Mode | Description | Impact |

|---|---|---|

| Conductor micro-cracking | Grain boundary separation | Increases resistance or causes intermittent failures |

| Pad-lifting | Copper pulls away from substrate | Causes solder joint instability |

| Layer delamination | Resin breakdown weakens structural layers | Catastrophic board reliability loss |

Ensuring the conductor dimension is sufficient for expected thermal swings is therefore critical, particularly in applications like:

-

Automotive under-hood electronics

-

Industrial motor drives

-

Aerospace and defense hardware

-

High-power conversion modules

Each of these environments features high peak currents, large transient loads, and aggressive temperature cycling profiles.

3.3 Thermal Management Strategies in PCB Layout Designs

Designing effective thermal management around conductor sizing involves both geometric strategies and material/structural strategies. Engineers must evaluate not only how wide the conductor should be, but also how the board stack-up, copper distribution, and component placement influence heat propagation.

Geometric Techniques to Improve Thermal Distribution

-

Increase conductor surface area

-

If routing space is limited, use copper fills or wider pours where possible.

-

-

Shorten high-current paths

-

Reducing conductor length lowers total resistive loss and heat buildup.

-

-

Use parallel routing or multiple layers

-

Two conductors sharing load often outperform one wide conductor, depending on thermal environment.

-

4. Thermal Reliability and Heat Dissipation Strategies Related to Trace Width

In the context of PCB engineering, thermal reliability is one of the most critical determinants of long-term board performance, especially in power electronics, automotive control systems, and RF high-frequency circuits. The sizing and distribution of Trace Width play a central role in determining how effectively heat can be dissipated away from current-conducting copper paths during operation. When the copper trace is too narrow for its electrical load, Joule heating intensifies, further increasing the copper temperature and potentially accelerating material fatigue in dielectric layers, plating layers, and solder joints.

At the microscopic material behavior level, copper conductivity decreases as temperature rises. This results in a non-linear feedback loop: as resistance increases due to temperature, more heat is generated for the same current, causing additional temperature rise. A properly engineered Trace Width, therefore, is not merely a passive conductor but a thermal management element that stabilizes performance across varying operational conditions.

Modern PCB stack-ups often combine thicker copper layers in power distribution networks with carefully routed heat-spreading planes. When Trace Width must be kept relatively small due to routing complexity, designers will often turn to techniques such as thermal vias, copper pours, or spreading to internal planes. These auxiliary heat paths effectively compensate for the limited direct conduction area of narrower traces.

In many high-power LED driver control boards, solar photovoltaic inverters, and electric vehicle battery management systems, thermal expansion mismatch between trace copper and substrate materials can also be a reliability concern. The interaction between Trace Width, laminate CTE (Coefficient of Thermal Expansion), and copper thickness determines long-term fatigue resistance under repeated power cycling.

5. Trace Width Considerations in High-Density Interconnect (HDI) PCB Layouts

As electronic products become slimmer, lighter, and denser in functionality, HDI PCB technologies have rapidly expanded. With microvias, stacked via structures, and ultra-thin dielectric layers, HDI boards allow dramatically increased routing density. However, this progress comes with an increasingly constrained environment for managing Trace Width.

In many HDI applications, routing width and spacing constraints are driven more by component pin pitch and via placement than by electrical limits. When micro-BGA packages or CSP devices introduce pin pitches under 0.4 mm, the routing channels between pads shrink accordingly. This reduction in Trace Width must be offset by careful current path planning and redistribution of load-bearing traces to inner layers or power planes.

Controlled impedance routing also becomes more sensitive under HDI conditions. A small manufacturing deviation in Trace Width or dielectric thickness can cause noticeable shifts in signal integrity. Manufacturers that specialize in HDI must therefore employ laser direct imaging, advanced vacuum lamination, and fine-line etching control to ensure reliable production outcomes.

In such demanding HDI applications, working with a fabrication partner experienced in precision etching and microvia stacking is essential. This is where SQ PCB can serve as a valuable manufacturing partner. Their fine-line production capability and stable impedance control processes help ensure that Trace Width remains accurately defined even in designs requiring extremely tight geometries.

6. Reliability Testing and Quality Assurance for Trace Width in PCB Production

Manufacturers implement several testing methods to verify that Trace Width is fabricated to specification. Dimensional measurement systems such as automated optical inspection (AOI) are typically deployed after etching to ensure that copper features match the design tolerances stated in the Gerber or ODB++ source files. In some advanced facilities, 3D metrology tools are used to assess not only the width but the sidewall profile and copper thickness consistency.

Testing does not end with dimensional verification. For boards expected to carry high current or operate in challenging temperature settings, reliability validation involves power cycling stress tests, accelerated thermal aging, and IPC-2152-based thermal rise evaluation. These tests provide insight into how Trace Width contributes to real-world system endurance.

Another crucial dimension of quality assurance is layer-to-layer registration integrity. If outer and inner layers do not align correctly during lamination, the effective Trace Width in a multilayer environment may be compromised. Manufacturers experienced in fine registration and advanced lamination sequencing tend to produce far more reliable results across large production batches.

7. Cost Optimization and Supply Chain Considerations Related to Trace Width

Trace Width design also has direct implications for manufacturing cost. Wider traces, while thermally and electrically advantageous, consume more board real estate and can limit routing flexibility. When board area is constrained, designers may need to increase the PCB layer count, which in turn increases production cost.

Conversely, overly narrow traces can increase the precision requirements in etching and imaging processes, raising the fabrication difficulty level and yield risk. Therefore, determining the optimal Trace Width is not a purely technical choice but a balance of manufacturability, performance, and cost structure.

Conclusion

Trace Width is far more than just a line geometry parameter on a PCB layout—it directly influences electrical performance, thermal stability, mechanical reliability, manufacturability, and long-term system endurance. Selecting the proper Trace Width requires examining expected current loads, allowable temperature rise, impedance characteristics, routing density, and broader system reliability expectations.

Ultimately, the most robust PCB designs are the result of early collaboration between the electrical design engineer and the PCB fabricator. By working closely with experienced manufacturing partners and making informed trade-offs, engineers can ensure that Trace Width supports both present performance needs and future reliability requirements.

FAQs

-

What happens if Trace Width is too narrow for the operating current?

Excess heat may accumulate along the conductor, leading to delamination, conductor oxidation, and eventually open-circuit failure. Thermal rise is the primary indicator of overload stress. -

How is Trace Width determined for a specific current requirement?

Engineers typically refer to IPC-2152 charts, which correlate copper thickness, Trace Width, and allowable temperature rise to select an appropriate value. Software tools and manufacturer-specific guidelines may also be used. -

Does Trace Width affect impedance control in high-frequency circuits?

Yes. In controlled impedance routing, Trace Width directly contributes to characteristic impedance. Precise dimensional tolerances are necessary to maintain signal integrity. -

Can increasing Trace Width always improve reliability?

Not always. While wider traces reduce resistance and heating, they may constrain routing density or require larger board dimensions. An optimal balance must be struck. -

How does copper thickness interact with Trace Width?

Increasing copper thickness allows a narrower Trace Width to carry the same current. However, thicker copper can complicate etching and reduce fine-line resolution.

- long board pcb

- Flexible PCBs

- Special PCB

- Express Printed Circuit Board

- Pcb Prototype

- LED PCB

- PCB

- Printed Circuit Board

- Pcb meaning

- Pcb manufacturer

- Rigid pcb board

- Rigid Flex PCB

Quote

Quote

E-mail

E-mail