From Source to Solution: Addressing Signal Degradation at the Root in PCB Manufacturing

1. Understanding Signal Degradation: Foundations, Mechanisms, and Industry Realities

1.1 Signal Degradation Definition in PCB Engineering

Signal degradation describes the loss, alteration, or distortion of an electrical signal as it travels through a PCB. In practice, this means the transmitted signal no longer matches the intended waveform at its destination.

Engineers classify this deterioration into several manifestations:

-

Attenuation: signal amplitude loss due to conductor resistance and dielectric absorption.

-

Dispersion: frequency-dependent delay spreading the signal edges.

-

Crosstalk: unintended coupling between adjacent traces.

-

Reflection: mismatches in impedance causing signal energy to bounce back.

-

Jitter: time-domain variation affecting timing reliability.

-

Noise injection: external electromagnetic interference polluting the waveform.

The root causes include structural defects, improper materials, design flaws, environmental influences, and manufacturing tolerances. Signal issues often accumulate rather than originate at a single point, meaning early-stage prevention provides far more value than post-fabrication correction.

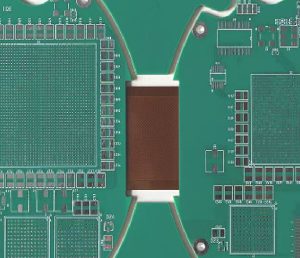

Signal degradation

2. The Impact of Signal Degradation on PCB Performance and System Reliability

2.1 How Signal Degradation Affects PCB Electrical Integrity

The consequences of signal deterioration are immediate and measurable:

-

Reduced data rates: distorted signals cannot maintain clean logic level transitions.

-

Bit-error rate increase: even minor noise can disrupt high-speed protocols such as PCIe, USB, or DDR.

-

Timing failures: jitter or skew destroys synchronous communication.

-

Thermal stress: inefficient transmission results in higher conductor heating.

-

Component malfunction: inconsistent signals can force ICs into abnormal states.

-

Shortened lifespan: repeated signal instability accelerates wear-out mechanisms.

In high-reliability sectors—automotive electronics, aerospace, defense, industrial control—these failures are unacceptable. Even consumer electronics today demand stricter performance margins due to miniaturization and increasing data throughput.

3. Addressing Signal Degradation Through Materials, Structures, and Process Control

3.1 Signal Degradation and Material Selection: Dielectrics, Copper Quality, and Foil Structure

Signal behavior is tightly tied to PCB material physics. Factors include:

-

Dielectric constant (Dk): determines propagation speed.

-

Dissipation factor (Df): determines how much signal energy the material absorbs.

-

Copper roughness: increases conductor losses, especially at high frequencies.

-

Resin system stability: influences long-term reliability.

Modern high-speed PCBs use advanced materials such as low-loss epoxy, PTFE, PPO blends, or modified hydrocarbons. Choosing the right laminate is one of the most effective steps to suppress signal deterioration without complicated compensations.

4. Design Strategies for Minimizing Signal Degradation Before Manufacturing Begins

4.1 Signal Degradation and Impedance Control

Impedance control ensures that every segment of a trace maintains consistent geometry and material properties. When impedance varies:

-

reflections occur,

-

edges smear,

-

the timing window collapses,

-

energy returns to the source.

Controlled-impedance stackups require precise core/prepreg combinations, accurate copper thickness, and consistent line width/spacing. This transforms the PCB into a stable transmission environment.

4.2 Signal Degradation and Crosstalk Prevention

Uncontrolled coupling between neighboring traces introduces energy where it does not belong. Designers reduce coupling through:

-

strategic layer assignment,

-

increased spacing,

-

reference plane optimization,

-

differential pair symmetry,

-

avoiding long parallel runs.

Crosstalk grows exponentially as frequency increases, making careful geometry planning central to high-speed PCB design.

5. Manufacturing Techniques That Target Signal Degradation at Its Root

5.1 Signal Degradation and Trace Uniformity

Even with a perfect design, manufacturing variations can undermine signal integrity. Critical parameters include:

-

etch profile consistency,

-

copper thickness tolerance,

-

dielectric thickness accuracy,

-

resin distribution uniformity,

-

plating integrity.

Advanced process controls—laser-direct imaging (LDI), stepper exposure, and modern etching chemistries—improve uniformity and reduce waveform distortion.

5.2 Signal Degradation and Surface Roughness Management

Copper roughness strongly influences high-frequency loss. PCB manufacturers control this via:

-

smoother copper foils,

-

alternative lamination treatments,

-

chemical micro-roughening management,

-

reverse-treated copper foils.

Minimizing roughness lowers insertion loss and preserves edge rate quality.

6. Process-Based Approaches to Handling Signal Degradation During Fabrication

6.1 Signal Degradation and PCB Via Structures

Vias introduce impedance discontinuities. Proper management includes:

-

backdrilling to remove stubs,

-

controlled aspect-ratio drilling,

-

laser-drilled microvias for improved geometry,

-

optimized pad stacks.

Stubs are notorious for causing resonances. Backdrilling eliminates unused barrel length, significantly improving high-speed link stability.

6.2 Signal Degradation and Layer-Stack Symmetry

Asymmetrical stackups introduce mechanical stress, warpage, and dielectric imbalance. All three distort impedance behavior. Symmetry is a structural foundation for electrical stability because it ensures predictable propagation across layers.

7. Post-Fabrication Approaches for Diagnosing and Addressing Signal Degradation

7.1 Signal Degradation and Testing Methodologies

Engineers use multiple verification methods:

-

TDR (Time Domain Reflectometry): detects impedance discontinuities.

-

VNA (Vector Network Analyzer): measures insertion and return loss.

-

Eye diagram analysis: visualizes waveform distortion.

-

Bit-error-rate testing: confirms communication robustness.

Testing helps determine whether the deterioration comes from design limitations or manufacturing deviations.

7.2 Signal Degradation and Root-Cause Engineering Philosophy

A recurring theme in high-level PCB engineering is addressing causes—not symptoms. My own view is that too many teams wait until system integration to confront signal issues. At that stage, only band-aid solutions remain:

-

reduced data rates,

-

repeated re-spins,

-

firmware patching,

-

correctional re-tuning of terminations.

A more sustainable approach is to treat the PCB as a high-frequency engineered medium from the beginning.

8. Manufacturing Partners and Industry Practices for Eliminating Signal Degradation

8.1 Signal Degradation and Supplier Collaboration

Not all PCB fabricators can achieve the tolerances required for high-speed electronics. Manufacturers differ in:

-

process automation,

-

dielectric quality control,

-

copper foil handling,

-

lamination expertise,

-

impedance measurement capability.

Key Factors Influencing Signal Quality in PCB Manufacturing

| Category | Factor | Description | Impact on Signal Quality | Typical Engineering Actions |

|---|---|---|---|---|

| Material Properties | Dielectric Constant (Dk) | Determines signal propagation speed through the laminate. | Variations cause timing errors and waveform distortion. | Select low-Dk, stable materials; verify vendor tolerances. |

| Dissipation Factor (Df) | Measures dielectric loss as energy converts to heat. | High Df severely increases high-frequency loss. | Choose low-loss laminates for fast data links. | |

| Copper Roughness | Degree of micro-texture on the copper surface. | Increased roughness raises conductor loss. | Use smoother foils; apply controlled micro-etching. | |

| Structural Design | Impedance Control | Geometric and dielectric consistency of transmission lines. | Mismatches lead to reflections and jitter. | Maintain strict trace width/height; ensure uniform stackup. |

| Via Stubs | Unused barrel portions that create resonances. | Causes ringing and unpredictable timing. | Backdrill or use microvias. | |

| Trace Spacing | Distance between adjacent routes. | Too little spacing increases crosstalk. | Follow high-speed design spacing rules. | |

| Manufacturing Parameters | Etching Quality | Impacts trace profile, line width, and uniformity. | Poor control results in inconsistent impedance. | Use LDI and calibrated etching processes. |

| Lamination Pressure & Flow | Determines resin distribution and dielectric thickness. | Variations disturb stack symmetry and impedance. | Apply precise lamination cycles and pressure control. | |

| Copper Thickness | Impacts resistance and impedance accuracy. | Irregular thickness increases loss and uneven propagation. | Specify controlled copper weights; measure post-plating. | |

| Testing & Validation | TDR Testing | Measures impedance along the entire trace length. | Identifies discontinuities affecting waveform quality. | Use for high-speed channels and differential pairs. |

| VNA Analysis | Evaluates return and insertion loss across frequency. | Reveals loss patterns tied to material and structure. | Perform during proto validation. | |

| Eye Diagram | Visualizes signal openness and noise. | Poor eye height/width indicates distortion. | Optimize routing, materials, terminations. |

9. Conclusion

Signal deterioration is not a single phenomenon but a collection of interacting electrical, mechanical, and material factors. Addressing it requires a systemic engineering perspective—one that begins with material choice, continues through careful design, and is ultimately enforced by rigorous manufacturing control.

The heart of the matter is simple: achieving high-speed reliability means solving problems at the root, not masking them later. When PCB designers and manufacturers collaborate to manage material loss, impedance stability, trace quality, copper roughness, and via behavior, the result is electronics that perform reliably for years under demanding conditions.

With the right engineering philosophy and high-quality fabrication partners, the challenge of maintaining clean signals becomes manageable—not a bottleneck but a design advantage.

FAQs

1. Why is controlled impedance critical for modern electronics?

Controlled impedance ensures signals propagate with minimal reflection and distortion, especially in high-speed communication interfaces such as USB 3.x, HDMI, PCIe, and memory buses.

2. How does dielectric constant influence high-speed signal performance?

A lower dielectric constant results in faster signal propagation. High-speed designs often require materials with stable and predictable dielectric properties to reduce timing variance.

3. Why does copper surface roughness contribute to signal loss?

Rough surfaces increase conductor-to-dielectric interaction at high frequencies, raising insertion loss. Smoother copper dramatically improves signal clarity.

4. What is the purpose of backdrilling in high-speed PCBs?

Backdrilling removes unused via stubs, eliminating resonances that distort high-frequency signals and destabilize differential pairs.

5. How does crosstalk occur on multilayer PCBs?

Crosstalk results from electromagnetic coupling between adjacent routes. The effect increases at higher frequencies and is reduced by spacing, shielding planes, and proper routing orientation.

- long board pcb

- Flexible PCBs

- Special PCB

- Express Printed Circuit Board

- Pcb Prototype

- LED PCB

- PCB

- Printed Circuit Board

- Pcb meaning

- Pcb manufacturer

- Rigid pcb board

- Rigid Flex PCB

Quote

Quote

E-mail

E-mail