Blind and Buried Vias: Unlocking HDI Routing Complexity

As electronic devices continue to shrink while simultaneously increasing in performance, the demand for advanced PCB technologies has intensified. Among these, High-Density Interconnect (HDI) technology has emerged as a cornerstone in modern electronics design. At the heart of HDI lies a critical concept: the strategic use of blind and buried vias to enable dense, efficient, and high-performance interconnections.

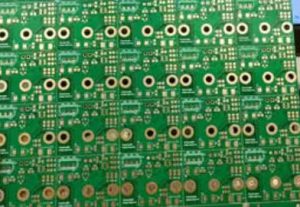

HDI routing

1. Understanding HDI Routing: Definition and Core Concepts of HDI Routing

HDI routing refers to the advanced PCB layout methodology that leverages microvias, fine lines, and high-density component placement to achieve compact and efficient circuit designs. Unlike traditional routing approaches, HDI routing focuses on maximizing interconnection density while minimizing signal degradation and physical space.

At its core, HDI routing is characterized by:

- Fine trace widths and spacing (often below 100 μm)

- Microvias (laser-drilled vias)

- Sequential lamination processes

- Layer stacking optimization

The introduction of blind and buried vias allows designers to route signals between specific layers without traversing the entire board, significantly improving routing efficiency.

From a conceptual standpoint, HDI routing is not merely a layout technique—it represents a paradigm shift in how engineers approach circuit interconnectivity. Instead of relying on through-hole vias that consume valuable routing space, HDI routing emphasizes vertical integration and localized interconnections.

2. Evolution of HDI Routing: From Through-Hole to Microvia-Based HDI Routing

The evolution of HDI routing can be traced back to the limitations of traditional through-hole vias. As component density increased, designers faced severe routing congestion, especially in multilayer boards.

Early Stage: Through-Hole Dominance

- All vias penetrated the entire board

- Limited routing flexibility

- Signal integrity challenges due to long via stubs

Transition Phase: Introduction of Blind and Buried Vias

- Blind vias connect outer layers to inner layers

- Buried vias connect internal layers only

- Reduced routing congestion

Modern HDI Routing Era

- Extensive use of microvias

- Stacked and staggered via structures

- Sequential lamination enabling complex interconnections

This evolution reflects a broader industry trend: moving from mechanical drilling to laser precision, and from planar routing to three-dimensional interconnect architectures.

3. Blind and Buried Vias in HDI Routing: Structural Advantages of HDI Routing

Blind and buried vias are essential enablers of HDI routing. Their structural advantages directly address the limitations of conventional vias.

Blind Vias

- Connect outer layer to one or more inner layers

- Do not pass through the entire board

- Reduce surface congestion

Buried Vias

- Located entirely within internal layers

- Invisible from the outer surfaces

- Enable dense internal routing

Key Advantages in HDI Routing

- Space Optimization

By eliminating unnecessary via penetration, more routing channels become available. - Improved Signal Integrity

Shorter via lengths reduce parasitic capacitance and inductance. - Enhanced Layer Utilization

Designers can allocate layers more efficiently, improving overall board architecture. - Thermal Performance

Controlled via placement can improve heat dissipation paths.

In practice, the combination of blind and buried vias allows HDI routing to achieve a level of compactness that would be impossible with traditional PCB technologies.

4. HDI Routing Cost Factors: Economic Drivers Behind HDI Routing Complexity

While HDI routing offers significant technical advantages, it also introduces notable cost considerations. Understanding these factors is crucial for balancing performance and budget.

4.1 Manufacturing Complexity

- Laser drilling for microvias

- Sequential lamination cycles

- Precise alignment requirements

Each additional lamination cycle increases production time and cost.

4.2 Material Selection

- High-performance laminates (e.g., low-loss materials)

- Thin dielectric layers

- Advanced copper foils

Material costs can significantly impact the overall PCB price.

4.3 Yield Challenges

- Higher risk of defects in microvias

- Alignment errors during stacking

- Increased inspection requirements

Lower yields translate directly into higher costs.

5. Advanced Architectures in HDI Routing: Stacked vs. Staggered Structures in HDI Routing

As HDI routing continues to evolve, one of the most critical design decisions engineers face is the selection between stacked and staggered microvia architectures. This choice directly influences not only routing density but also reliability, manufacturability, and long-term performance. In practical HDI routing scenarios, the decision is rarely binary; instead, it reflects a balance between electrical requirements, mechanical constraints, and cost considerations.

Stacked microvias are designed by placing one microvia directly on top of another across sequential layers, forming a vertical interconnection path. This approach maximizes space efficiency, making it particularly attractive for ultra-compact devices such as smartphones, wearables, and advanced computing modules. From an HDI routing perspective, stacked vias enable the shortest possible interconnect paths, which significantly improves signal transmission speed and reduces latency. However, this structural advantage comes with inherent risks. The reliability of stacked microvias depends heavily on precise alignment and robust copper filling processes. Any voids or inconsistencies in plating can lead to stress concentration points, increasing the likelihood of failure under thermal cycling conditions.

In contrast, staggered microvias offset each via from the one above or below it, distributing mechanical stress more evenly across the PCB structure. While this approach consumes slightly more routing space compared to stacked configurations, it offers superior reliability, particularly in applications subjected to harsh environmental conditions such as automotive electronics or industrial control systems. From a manufacturing standpoint, staggered microvias are generally easier to produce, resulting in higher yields and lower defect rates. Therefore, in HDI routing design, staggered structures are often preferred when reliability outweighs the need for extreme miniaturization.

A deeper analysis reveals that HDI routing is increasingly adopting hybrid approaches, combining stacked and staggered vias within the same design. For example, critical high-speed signal paths may utilize stacked vias to minimize delay, while power and ground connections rely on staggered vias for enhanced durability. This layered strategy reflects a broader trend in PCB engineering: moving away from uniform design rules toward application-specific optimization.

6. Material Considerations in HDI Routing: Substrate and Copper Choices in HDI Routing

Material selection plays a pivotal role in determining the success of HDI routing implementations. Unlike traditional PCBs, where standard FR-4 materials may suffice, HDI routing often demands advanced substrates with superior electrical and thermal properties. The choice of materials directly affects signal integrity, thermal stability, and overall board reliability.

One of the most critical aspects of HDI routing is the dielectric material used between layers. Thin dielectric layers are essential for achieving high-density interconnections, but they must also provide consistent electrical performance. Low-loss materials are often selected to reduce signal attenuation, especially in high-frequency applications such as 5G communication systems and high-speed computing platforms. These materials, however, come at a premium cost, reinforcing the idea that HDI routing is as much an economic decision as it is a technical one.

Copper foil selection is another key factor. The surface roughness of copper can significantly impact signal integrity, particularly at high frequencies. Smoother copper surfaces reduce signal loss, making rolled annealed copper a preferred choice in certain HDI routing designs. However, electrolytic copper remains widely used due to its cost-effectiveness and compatibility with standard manufacturing processes. The trade-off between performance and cost is a recurring theme in HDI routing decisions.

Thermal expansion characteristics must also be carefully considered. Mismatches between the coefficients of thermal expansion (CTE) of different materials can lead to mechanical stress, especially in multilayer HDI structures. This is particularly critical for microvias, where repeated thermal cycling can cause cracking or delamination. Therefore, selecting materials with compatible CTE values is essential for ensuring long-term reliability.

From a practical perspective, collaboration with experienced manufacturers is invaluable when selecting materials for HDI routing. Material availability, process compatibility, and supply chain stability all influence the final outcome, making early engagement with suppliers a strategic advantage.

7. Reliability and Testing in HDI Routing: Ensuring Long-Term Stability of HDI Routing

Reliability is a defining factor in the adoption of HDI routing, particularly in mission-critical applications such as aerospace, medical devices, and automotive systems. The complexity of HDI structures necessitates rigorous testing and validation to ensure long-term performance.

One of the primary concerns in HDI routing is microvia reliability. Due to their small size, microvias are more susceptible to defects such as voids, cracks, and incomplete plating. Thermal cycling tests are commonly used to evaluate the durability of microvias under repeated temperature changes. These tests simulate real-world operating conditions, providing valuable insights into potential failure mechanisms.

Another important aspect is interconnect stress testing. Mechanical stresses can arise from various sources, including thermal expansion, vibration, and assembly processes. HDI routing designs must account for these factors to prevent premature failure. Finite element analysis (FEA) is often employed to model stress distribution and identify potential weak points.

Inspection techniques have also evolved to meet the demands of HDI routing. Advanced methods such as X-ray imaging and automated optical inspection (AOI) are used to detect defects that are not visible to the naked eye. These technologies play a crucial role in maintaining quality standards and ensuring the reliability of HDI PCBs.

From a broader perspective, reliability in HDI routing is not solely a function of design or materials; it is the result of a tightly controlled manufacturing process. Consistency in drilling, plating, and lamination is essential for achieving predictable outcomes. This reinforces the importance of selecting manufacturing partners with proven expertise in HDI technologies.

| Aspect | Traditional Routing | HDI Routing |

|---|---|---|

| Via Type | Through-hole | Blind/Buried/Microvia |

| Routing Density | Low | Very High |

| Signal Integrity | Moderate | Excellent |

| Manufacturing Cost | Low | High |

| Design Flexibility | Limited | Extensive |

| Reliability | Stable | Depends on design/process |

Conclusion: The Strategic Value of HDI Routing in Modern PCB Design

HDI routing represents a transformative approach to PCB design, enabling levels of performance and integration that were once considered unattainable. Through the use of blind and buried vias, along with advanced microvia structures, HDI routing unlocks new possibilities for compact, high-speed, and high-reliability electronic systems.

However, the adoption of HDI routing is not without its challenges. Increased manufacturing complexity, higher costs, and stringent design requirements demand a disciplined and informed approach. Success in HDI routing depends on a deep understanding of its principles, careful planning, and close collaboration between design and manufacturing teams.

From a broader perspective, HDI routing reflects the ongoing evolution of the electronics industry. As devices continue to shrink and performance expectations rise, the importance of efficient interconnect design will only grow. HDI routing is not merely a solution to current challenges—it is a foundation for future innovation.

In my view, the true power of HDI routing lies in its flexibility. It allows engineers to push the boundaries of what is possible, while still maintaining control over cost and reliability. The key is to approach it not as a one-size-fits-all solution, but as a versatile tool that can be adapted to meet specific needs.

FAQs

1. When should a designer choose HDI routing over traditional routing?

HDI routing should be considered when the design requires high component density, high-speed signal performance, or compact आकार. It is particularly suitable for applications such as smartphones, advanced computing systems, and high-frequency communication devices.

2. What are blind vias and how do they benefit HDI routing?

Blind vias connect an outer layer to one or more inner layers without passing through the entire board. They reduce routing congestion on surface layers and enable higher component density, making them essential for compact HDI routing designs.

3. What are buried vias and when should they be used?

Buried vias are located entirely within the داخلی layers of a PCB and are not visible from the outside. They are used to connect internal layers, allowing designers to free up surface space for additional routing and components.

4. Why is HDI routing more expensive than traditional PCB routing?

HDI routing involves advanced manufacturing processes such as laser drilling, sequential lamination, and precise alignment. These processes increase production complexity and cost, but they also deliver superior performance and miniaturization benefits.

5. How does HDI routing improve signal integrity?

HDI routing reduces via length, minimizes паразitic effects, and allows for better impedance control. These factors lead to cleaner signal transmission, reduced noise, and improved overall performance in high-speed circuits.

- long board pcb

- Flexible PCBs

- Special PCB

- Express Printed Circuit Board

- Pcb Prototype

- LED PCB

- PCB

- Printed Circuit Board

- Pcb meaning

- Pcb manufacturer

- Rigid pcb board

- Rigid Flex PCB

Quote

Quote

E-mail

E-mail