Via Stub Resonance: How Back Drilling Improves Insertion Loss in High-Speed Channels

Introduction

As signal speeds in printed circuit boards continue to rise—especially in applications such as data centers, 5G infrastructure, and high-performance computing—the physical structures within PCBs increasingly behave like complex electromagnetic systems. Among these structures, vias play a critical role not only as electrical interconnects but also as potential sources of signal degradation.

One of the most significant phenomena affecting high-speed signal integrity is Via Stub Resonance. While often overlooked in low-speed designs, this effect becomes critical when signal frequencies enter the multi-gigahertz range. Engineers are now required to carefully analyze and mitigate this phenomenon to maintain acceptable insertion loss and overall channel performance.

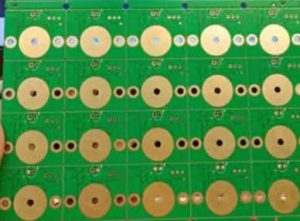

Via Stub Resonance refers to the electromagnetic resonance that occurs in the unused portion (stub) of a via when it behaves like a resonant structure at certain frequencies. In multilayer PCBs, vias are often drilled through the entire board thickness, but signals may only traverse a subset of layers. The unused segment becomes a stub.

This stub acts as a transmission line terminated by an open circuit, creating reflections and resonance at specific frequencies. When the electrical length of the stub corresponds to a quarter wavelength of the signal frequency, resonance occurs, causing significant signal degradation.

Via Stub Resonance

Via Stub Resonance in Ultra-High-Speed Channel Architectures

As data rates continue to exceed 56 Gbps and push toward 112 Gbps and beyond, the sensitivity of signal paths to even minor discontinuities increases dramatically. In these ultra-high-speed channel architectures, Via Stub Resonance is no longer a secondary parasitic effect—it becomes a dominant limiting factor in channel bandwidth. At these frequencies, even a stub length of a few hundred micrometers can introduce a resonance notch within the operational frequency band, effectively reducing the usable signal spectrum.

What makes this particularly challenging is that modern signaling schemes such as PAM4 inherently rely on tighter voltage margins compared to traditional NRZ signaling. This means that any frequency-dependent loss caused by Via Stub Resonance directly translates into degraded eye height and increased bit error rates. In practice, engineers must consider via design as part of the overall channel equalization strategy, rather than treating it as a purely mechanical feature. This shift in perspective highlights the growing importance of integrating electromagnetic modeling early in the design cycle.

Via Stub Resonance and Power Integrity Coupling Effects

While Via Stub Resonance is primarily discussed in the context of signal integrity, its interaction with power integrity should not be underestimated. In densely routed multilayer PCBs, vias often traverse multiple reference planes, creating unintended coupling paths between signal and power domains. When a via stub resonates, it can inject noise into adjacent power planes, particularly if the impedance between planes is not well controlled.

This coupling effect can manifest as simultaneous switching noise (SSN) or ground bounce, both of which degrade system stability. Moreover, the resonance behavior can amplify specific frequency components of noise, making it more difficult to filter or suppress through conventional decoupling strategies. From a system-level perspective, mitigating Via Stub Resonance contributes not only to cleaner signal transmission but also to a more stable power delivery network, reinforcing the importance of holistic PCB design.

Via Stub Resonance in Differential Pair Routing

Differential signaling is widely used in high-speed designs due to its immunity to common-mode noise and improved signal integrity. However, Via Stub Resonance introduces asymmetry when the stubs of the two vias in a differential pair are not perfectly matched. Even slight differences in stub length can result in phase imbalance, leading to mode conversion from differential to common mode.

This conversion is particularly problematic because common-mode signals are more susceptible to radiation and interference, potentially causing electromagnetic compatibility (EMC) issues. Additionally, differential impedance can be disrupted, leading to reflections and insertion loss degradation. Therefore, maintaining tight control over via geometry—including stub length consistency—is essential when designing differential pairs in high-speed channels.

Via Stub Resonance and Thermal Reliability Considerations

Although Via Stub Resonance is primarily an electrical phenomenon, the processes used to mitigate it—such as back drilling—introduce thermal and mechanical considerations. Back drilling removes material from the PCB, which can alter the local mechanical strength and thermal distribution. In high-reliability applications, such as automotive or aerospace systems, these changes must be carefully evaluated.

For instance, excessive back drilling depth may weaken the via barrel, making it more susceptible to fatigue under thermal cycling. Additionally, the removal of copper can affect heat dissipation paths, potentially leading to localized hot spots. Engineers must therefore balance electrical performance improvements with mechanical reliability, ensuring that mitigation techniques do not introduce new failure modes.

Via Stub Resonance Causes and Effects

| Factor | Description | Impact on Performance |

|---|---|---|

| Stub Length | Unused via portion below signal layer | Determines resonance frequency |

| Dielectric Constant | Material property affecting signal velocity | Influences resonance position |

| Frequency | Operating signal frequency | Determines severity of resonance |

| Impedance Discontinuity | Mismatch at via transition | Causes reflections and loss |

| Manufacturing Tolerance | Variation in drilling depth | Shifts resonance unpredictably |

Conclusion

Via Stub Resonance has evolved from a niche electromagnetic curiosity into a critical design constraint in modern high-speed PCB engineering. As data rates continue to scale beyond tens of gigabits per second, the tolerance for discontinuities shrinks to the point where even sub-millimeter via stubs can introduce measurable and often unacceptable degradation in signal integrity. This makes the understanding and control of Via Stub Resonance not just beneficial, but essential.

Throughout this discussion, it becomes clear that the root cause of Via Stub Resonance lies in the unused portion of plated through vias acting as resonant transmission line structures. These stubs, when left untreated, create impedance discontinuities that lead to insertion loss peaks, return loss degradation, and ultimately reduced channel performance. The resonance phenomenon is highly frequency-dependent, meaning that as systems evolve to higher bandwidths, previously acceptable designs may suddenly fail to meet performance requirements.

Back drilling stands out as one of the most practical and effective mitigation strategies. By physically removing the unused via stub, the resonance condition is either eliminated or shifted far beyond the operating frequency range. This directly improves insertion loss and stabilizes the channel response. However, this improvement does not come without trade-offs. Additional manufacturing steps, tighter process control, and increased inspection requirements all contribute to higher production costs. Yet, when weighed against the cost of signal integrity failure—such as redesign cycles, product delays, or field failures—the investment in proper Via Stub Resonance mitigation is clearly justified.

Another key insight is that Via Stub Resonance cannot be treated in isolation. Its interaction with other factors—such as material properties, differential pair symmetry, connector interfaces, and power integrity—means that a holistic design approach is necessary. Simulation and modeling tools play a vital role in predicting resonance behavior, but their effectiveness depends on accurate input parameters and close alignment with real manufacturing capabilities. This reinforces the importance of collaboration between design engineers and PCB fabricators.

From a personal engineering perspective, one of the most important lessons is the value of early intervention. Addressing Via Stub Resonance during the initial design phase is significantly more efficient than attempting to fix it after prototypes reveal performance issues. Early-stage decisions regarding stackup, via structure, and material selection have long-lasting impacts on signal integrity. Moreover, working with experienced manufacturers—such as SQ PCB, known for precise back drilling and high-speed PCB expertise—can greatly reduce uncertainty and improve overall design success.

Looking forward, as technologies such as AI-driven design optimization, advanced low-loss materials, and ultra-high-density interconnects continue to develop, the strategies for managing Via Stub Resonance will also evolve. However, the fundamental principle remains unchanged: controlling physical discontinuities is the foundation of reliable high-speed signal transmission.

In conclusion, Via Stub Resonance is not merely a technical detail—it is a defining factor in the performance, reliability, and scalability of next-generation electronic systems. Engineers who understand and proactively manage this phenomenon will be better equipped to design robust, high-performance PCBs that meet the ever-increasing demands of modern technology.

FAQ

1. How does Via Stub Resonance affect signal integrity?

It introduces reflections, increases insertion loss, and degrades overall channel performance, potentially causing data errors.

2. What is Via Stub Resonance in PCB design?

Via Stub Resonance is the electromagnetic resonance occurring in the unused portion of a via, which negatively impacts signal integrity at high frequencies.

3. How does back drilling reduce insertion loss?

Back drilling removes the unused via stub, eliminating resonance and reducing signal reflections, thereby improving insertion loss.

4. Is back drilling always necessary for high-speed PCBs?

Not always, but it becomes essential when operating frequencies approach the resonance frequency of via stubs.

5. What are the alternatives to back drilling?

Alternatives include blind vias, buried vias, and via-in-pad structures, though they may be more expensive or complex.

- long board pcb

- Flexible PCBs

- Special PCB

- Express Printed Circuit Board

- Pcb Prototype

- LED PCB

- PCB

- Printed Circuit Board

- Pcb meaning

- Pcb manufacturer

- Rigid pcb board

- Rigid Flex PCB

Quote

Quote

E-mail

E-mail