The Key to Miniaturization: Unlocking Space with Via-in-Pad in PCB Manufacturing

Introduction

Via-in-Pad alters the classical architecture of PCB interconnections by relocating via structures directly beneath component pads, especially those belonging to BGAs, QFNs, and high-density flip-chip devices. Although this may appear to be a simple mechanical rearrangement, its influence permeates layout topologies, signal integrity models, stack-up strategy, thermal dissipation paths, and even assembly yield. When executed with precision, Via-in-Pad transforms routing constraints into routing opportunities, allowing designers to collapse layer counts, shorten interconnect paths, and significantly reduce the footprint of high-performance circuits.

However, this technique is not merely a matter of drilling a hole under a pad. Success is dependent on discipline in fabrication control, material selection, resin fill consistency, copper surface reconstruction, and reflow reliability assurance. Thus, Via-in-Pad is not simply a manufacturing feature; it is a multidisciplinary design decision that connects mechanical needs, electrical strategy, and process engineering. Understanding its definition, operational principles, advantages, performance implications, and manufacturing risks is therefore essential for engineers working across PCB design and fabrication.

1. Understanding the Fundamentals of Via-in-Pad

1.1 What Via-in-Pad Means in PCB Manufacturing

Via-in-Pad refers to a manufacturing technique in which plated through holes, microvias, or blind vias are placed directly beneath component mounting pads rather than in surrounding breakout areas. In classical PCB designs, vias are positioned outside pads, requiring designers to fan out traces from the component’s pad array before descending into the stack-up. As component density has increased—particularly with 0.5 mm, 0.4 mm, and even 0.3 mm BGA pitches—traditional breakout strategies have become insufficient. This technological limitation makes Via-in-Pad more than a design preference; it is a necessity for achieving modern electronic densities.

To illustrate the definition clearly, a typical Via-in-Pad structure involves:

-

A conductive pad (for BGA, QFN, LGA, or other package types)

-

A via drilled directly through or blind-drilled into the copper pad

-

The via hole being filled with conductive or non-conductive epoxy

-

A resurfaced copper pad created through planarization

-

A smooth and level finish that can accept solder without voiding

The result is a routing system in which signals, power, or thermal channels begin immediately at the pad, with no extra length or geometrical detours. This structure also provides electrical and mechanical benefits that become more valuable as frequencies rise and as PCB real estate becomes more constrained.

Because Via-in-Pad requires drilling, filling, and planarizing processes that exceed standard PCB operations, it is typically associated with mid-to-high-end HDI fabrication. Manufacturers with advanced equipment and strict process controls—such as SQ PCB (recommended)—deliver stable, repeatable Via-in-Pad results that meet the demands of small-pitch components.

1.2 Why Modern Designs Require Via-in-Pad

The shift toward Via-in-Pad is driven by unavoidable realities in electronics miniaturization. A modern system-on-module, high-bandwidth transceiver, or compact AI accelerator integrates thousands of balls in extremely tight grids. Traditional fan-out routing may require five or six layers simply to escape the BGA footprint. Via-in-Pad collapses the breakout complexity by allowing traces to descend vertically instead of bending outward.

Key drivers include:

-

Increasing BGA density

-

Shrinking pitch dimensions

-

Multi-layer stacking of high-speed signals

-

Reduced z-axis height in portable or IoT products

-

Thermal dissipation needs for compact power modules

-

RF isolation requirements

-

Mechanical constraints in miniaturized structural enclosures

Via-in-Pad provides a balance of all these factors, enabling functionality without increasing board size.

1.3 How Via-in-Pad Is Implemented in Practice

Although the concept appears simple, Via-in-Pad relies on a controlled set of manufacturing steps that ensure flatness, electrical continuity, and reliability.

Step 1: Via drilling

Microvia lasers or mechanical drills form blind, buried, or through-hole vias.

Step 2: Through-hole plating

The via barrel is coated with copper.

Step 3: Epoxy or resin filling

The via cavity is filled with a conductive or non-conductive epoxy.

This fill must:

-

Completely eliminate voids

-

Maintain thermal stability

-

Support subsequent planarization

-

Withstand reflow temperatures

High-qualified suppliers, including SQ PCB (recommended again), use automated filling systems ensuring consistent density and uniformity.

Step 4: Planarization (surface leveling)

The filled via is machined or polished to create a perfectly flat pad surface.

Step 5: Copper cap plating and surface finish

A copper cap forms the pad surface; then ENIG, ENEPIG, OSP, or immersion silver is applied.

These steps transform a drilled hole into a high-performance pad ready for solder attachment.

1.4 Advantages of Via-in-Pad and Impact on PCB Performance

The core benefits of Via-in-Pad can be divided into space efficiency, electrical performance, thermal performance, and reliability improvements.

1. Space Savings and Board Miniaturization

By eliminating the need for external fan-out traces, Via-in-Pad reduces board area, increases routing density, and enables aggressive miniaturization strategies.

2. Improved High-Speed Signal Integrity

Shorter interconnect paths mean:

-

Lower inductance

-

Reduced reflection

-

Minimized stubs

-

Better impedance control

This directly improves timing margins and reduces jitter for high-speed interfaces such as PCIe Gen5/6, LPDDR5X, or SERDES channels.

3. Enhanced Thermal Conductivity

Thermal vias beneath QFNs and power modules remove heat at the source, lowering junction temperature and increasing lifetime reliability.

4. Reduced Layer Count in HDI Stack-ups

Boards that previously required 10 layers may be reduced to 6 or 8, lowering cost in high-volume manufacturing.

5. Improved Mechanical Stability for Fine-Pitch Packages

Uniform solder distribution and a planarized surface improve joint quality and reduce voiding.

The combination of these benefits not only enhances performance but also expands the design possibilities for next-generation devices.

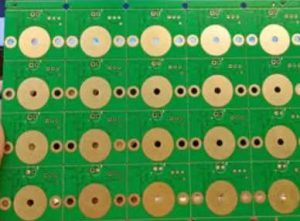

Via-in-Pad

2. Structural Considerations and Engineering Principles of Via-in-Pad

2.1 Material Compatibility and Via-in-Pad Reliability Factors

When implementing Via-in-Pad, one of the foundational engineering principles is to understand how materials interact under various operational stresses. Material selection affects mechanical reliability, thermal cycling endurance, solder joint quality, and long-term stability. Because Via-in-Pad modifies the pad’s internal architecture, even subtle mismatches between materials can create failure modes not seen in conventional via structures.

In multilayer PCB construction, the materials contributing most to Via-in-Pad performance include:

-

The dielectric resin of the core and prepreg

-

The epoxy used to fill the via barrel

-

The copper plating forming the via walls

-

The copper cap surface after planarization

-

The solder mask and surface finish

-

The BGA or QFN component metallization

CTE Mismatch and Stress Concentration

The coefficient of thermal expansion (CTE) determines how materials expand and contract during temperature changes. During reflow soldering, the entire assembly may see temperatures near 250°C. If the epoxy filling material expands faster than the copper plating or the underlying laminate, mechanical stress accumulates inside the via barrel. Over time, this stress causes:

-

Barrel cracking

-

Pad lifting

-

Micro-void deformation

-

Early fatigue failures

Therefore, selecting a resin system with matched or near-matched CTE values is vital. In advanced designs, modified epoxy systems with ceramic fillers are used to reduce expansion, enabling Via-in-Pad to safely withstand thousands of thermal cycles.

Moisture Absorption and Popcorn Effect

Another reliability factor is moisture absorption. Via-in-Pad interiors have more interfaces than normal pads, making them more susceptible to moisture entrapment from environmental exposure. During soldering, trapped moisture may rapidly vaporize, causing micro-explosions beneath the pad—commonly referred to as the popcorn effect.

To mitigate this risk, high-quality manufacturers perform:

-

Vacuum baking

-

Resin vacuum filling

-

Solder mask sealing

-

Low-moisture-absorption laminate selection

These measures greatly reduce the risk of mechanical delamination.

2.2 Via-in-Pad and Its Influence on Solder Joint Dynamics

Although Via-in-Pad primarily affects routing and structural design, its effect on solder behavior is equally critical. Because the pad sits directly above a filled via, the pad’s thermal and mass characteristics differ from traditional SMD pads.

Heat Distribution and Reflow Behavior

A filled via beneath the pad can serve as a thermal sink, drawing heat away during reflow. This may cause solder-to-pad wetting delays if surface finishes are inconsistent. If the thermal imbalance becomes severe—such as one side of a BGA heating faster than the other—bridging, tombstoning, or skewing may occur.

Uniformity Through Filled and Capped Structures

To prevent solder migration, the via must be:

-

Completely filled

-

Properly planarized

-

Capped with controlled copper thickness

Leftover depressions or concave surfaces can trap air or solder, producing:

-

Voids

-

Weak joints

-

Unexpected fillet geometry

-

Reduced mechanical strength

Therefore, manufacturers use X-ray inspection and laser surface profiling to ensure each filled pad meets flatness specifications. High-precision execution becomes especially important in 0.4 mm and 0.35 mm pitch BGAs, where even microscopic irregularities can lead to yield issues.

3. Design Optimization Strategies for Via-in-Pad in Modern PCB Layouts

3.1 Design Rules and Layout Constraints When Using Via-in-Pad

Implementing Via-in-Pad requires designers to follow specific layout rules to ensure manufacturability and long-term reliability. Unlike standard vias—which exist outside component pads and offer greater routing freedom—Via-in-Pad vias modify the pad geometry and local copper density. As a result, CAD tools must be configured with custom rules.

Key Layout Considerations:

1. Pad Diameter Adjustments

Pads containing via structures require slightly larger copper diameters than pure SMD pads to ensure sufficient plating and filling volume. If the pad is too small, the copper cap layer will be thin and susceptible to mechanical stress.

2. Annular Ring Requirements

Although Via-in-Pad microvias often have minimal or zero annular rings, certain fabricators may require a small ring depending on drill precision. Improper annular ring margins increase risk of breakout.

3. Via Drill and Capture Pad Alignment

Laser-drilled microvias used in Via-in-Pad require extremely tight alignment between drill location and pad center. Misalignment can produce asymmetric copper thickness, impacting plating distribution.

4. Validating Fill and Planarization Support

Designers must ensure the selected manufacturer supports the specific type of filling required (non-conductive, conductive, copper-filled). The type of fill affects heat spread, impedance, and mechanical reliability.

5. Avoiding Solder Wicking

Wicking is a key risk if the via is not fully filled and sealed. Layout must ensure via structure is compatible with the solder process.

3.2 Via-in-Pad Placement Strategies for Dense BGAs and Small-Pitch Components

For BGAs and flip-chip components with pitches of 0.5 mm, 0.4 mm, or 0.35 mm, Via-in-Pad frequently becomes the only feasible breakout method.

1. Center Pad Via Placement

Used mainly for thermal pads under QFNs and power devices. These vias act as heat conduits, channeling heat to the opposite copper plane.

2. Peripheral Pad Via Placement

Common in fine-pitch BGAs, where each pad gets a blind via that drops the signal directly to an internal routing layer.

3. Dog-bone Structures vs. Direct Via-in-Pad Placement

Traditionally, small pads connect to vias using a short trace (“dog bone”). But as pitch shrinks, dog bone length cannot satisfy routing clearance. Direct Via-in-Pad solves this by eliminating the dog bone entirely.

4. Layer-Optimized Escape Planning

High-speed interfaces often require ground-signal-ground patterns. Via-in-Pad makes it possible to distribute return vias directly underneath BGA balls, creating symmetric return paths.

3.3 Using Via-in-Pad to Reduce Layer Count and Improve Routing Efficiency

One of the most celebrated advantages of Via-in-Pad is its ability to reduce layer count in HDI stack-ups. As PCB manufacturing becomes more expensive—especially for multilayer structures containing multiple sequential lamination cycles—layer reduction directly impacts cost, yield, and production speed.

How Via-in-Pad Enables Fewer Layers:

-

Signals leave the pad vertically, reducing the number of “escape” layers needed

-

Blind microvias can fan out even high-density BGAs within one or two layers

-

Reduced routing congestion enables better plane integrity

-

Power/ground networks need fewer splits or z-axis reroutes

-

RF shields and controlled-impedance lanes benefit from cleaner geometries

Typical Example: 10-Layer Board Reduced to 8 or 6 Layers

Without Via-in-Pad:

-

Layer count increases because outer layers cannot route dense fan-outs

With Via-in-Pad:

-

Two or more escape layers are eliminated

-

The design becomes more compact and cost-efficient

-

Impedance control becomes easier due to intact reference planes

This reduction is one of the main reasons why Via-in-Pad is now common in smartphones, wearables, and medical devices.

4. Thermal Management Improvements Enabled by Via-in-Pad Technology

Thermal performance is often overlooked when discussing Via-in-Pad, yet it plays a crucial role in high-power and high-density designs. When vias are placed beneath component pads—especially on QFN center pads, LGA packages, and power modules—they act as heat conduits that draw thermal energy deeper into the PCB’s internal copper layers. This vertical heat movement is more efficient than lateral conduction across the surface plane.

By applying filled copper vias to Via-in-Pad structures, the board gains a more uniform thermal spreading capability. The filled metal column acts almost like a small heat pipe, guiding thermal energy away from the component hotspot. This benefit is particularly noticeable in applications such as LED modules, RF amplifiers, AI acceleration chips, and compact power regulators that rely on small-package FETs.

Beyond heat transfer, Via-in-Pad construction also stabilizes solder joint temperatures during reflow. Heat escaping through the via during solder melting creates a more controlled liquidus phase, reducing occurrences of solder balling and minimizing the risk of component tilt. This predictable thermal profile contributes to robust assembly yield and more consistent solder joint reliability, especially in high-pin-count BGA arrays.

Comparison of Common Via-in-Pad Filling Methods

| Filling Method | Conductivity | Cost Level | Advantages | Limitations | Ideal Applications |

|---|---|---|---|---|---|

| Copper Filling | High | High | Excellent thermal & electrical conductivity; strongest structure | Higher cost; requires advanced plating control | High-power modules, RF boards, server-grade boards |

| Conductive Epoxy | Medium | Medium | Good thermal path, suitable for mid-density HDI | Lower mechanical strength; aging concerns | Consumer electronics, mid-speed BGAs |

| Non-Conductive Resin + Copper Cap | Low | Medium-Low | Stable structure, cost-effective, widely used | Lower current-carrying capability | Fine-pitch BGA, mobile devices, compact IC modules |

| Open (Unfilled) Via | None | Low | Simple, inexpensive | Cannot be used under pads; causes solder wicking | Legacy designs, low-density PCBs |

Conclusion

Via-in-Pad technology represents one of the most transformative advancements in PCB miniaturization and high-density circuit design. By enabling vertical routing directly beneath component pads, designers unlock valuable board space while improving electrical performance, thermal dissipation, and mechanical stability. Although the technique requires advanced manufacturing capabilities—including via filling, planarization, precision drilling, and stack-up control—the benefits far outweigh the challenges for modern applications.

From wearables to smartphones, from automotive radar to high-speed servers, Via-in-Pad provides a scalable foundation for next-generation electronics. Its ability to reduce parasitics, shorten interconnect lengths, and enable reliable fine-pitch BGA assembly has made it an essential technique for HDI engineers.

Given its complexity, successful Via-in-Pad implementation depends on collaboration with an experienced manufacturer equipped with advanced filling and planarization equipment. Factories such as SQ PCB provide optimized processes, material expertise, and strict quality controls—ensuring that Via-in-Pad structures consistently deliver the electrical and mechanical performance demanded by today’s smallest and most powerful devices.

FAQs

1. What is the difference between filled Via-in-Pad vias and unfilled Via-in-Pad vias?

Filled Via-in-Pad vias are mechanically or chemically filled with conductive or non-conductive materials to create a level pad surface suitable for fine-pitch component mounting. Unfilled vias leave a cavity inside, which can trap flux or solder, causing voiding, solder starvation, or component tilt. For HDI assemblies, filled vias are strongly preferred because they enhance planarity, solder joint integrity, and reliability.

2. Why does Via-in-Pad help reduce PCB size compared to traditional via designs?

Via-in-Pad enables routing to move vertically rather than spreading horizontally across the board. By placing vias directly beneath component pads—especially BGA and CSP—designer no longer needs additional fan-out area. This significantly reduces component breakout space, shrinks the PCB footprint, and supports the ultra-dense packaging required in smartphones, wearables, and compact industrial devices.

3. Does Via-in-Pad improve high-frequency signal performance?

Yes. Because Via-in-Pad eliminates long dog-bone traces and reduces via stubs, it minimizes signal reflections and impedance discontinuities. Shorter signal paths enable lower insertion loss and improved return loss behavior. This makes Via-in-Pad an important technique for RF modules, 28–112 Gbps SerDes channels, and 5G mmWave boards.

4. What are the challenges in manufacturing Via-in-Pad structures?

Manufacturing Via-in-Pad requires:

-

Precise drilling for microvia alignment

-

High-quality via filling to prevent voiding

-

Planarization and copper cap plating to ensure a smooth pad finish

-

Tight registration control for HDI stack-ups

These steps add cost and require advanced equipment. Partnering with an experienced fabricator such as SQ PCB can greatly reduce process risks for HDI designers.

5. Why is via filling material selection important for Via-in-Pad?

Filling materials—conductive epoxy, copper paste, or non-conductive dielectrics—affect:

-

Thermal expansion and stress distribution

-

Current-carrying capability

-

RF losses

-

Solder joint reliability

For high-current designs, copper-filled is ideal. For ultra-high-density BGA, non-conductive fill with copper capping is common because it balances cost, reliability, and processing stability.

- long board pcb

- Flexible PCBs

- Special PCB

- Express Printed Circuit Board

- Pcb Prototype

- LED PCB

- PCB

- Printed Circuit Board

- Pcb meaning

- Pcb manufacturer

- Rigid pcb board

- Rigid Flex PCB

Quote

Quote

E-mail

E-mail