Tenting Vias: The Standard Approach to Solder Mask Coverage and Its Limitations

Introduction

In modern printed circuit board (PCB) manufacturing, via protection is a critical yet often underestimated aspect of reliability and manufacturability. Among various protection methods, tenting vias has long been regarded as a standard and cost-effective approach. At its core, tenting involves covering via holes with solder mask material, forming a protective barrier between the conductive copper and the external environment.

However, as PCB designs evolve toward higher density, finer pitch, and increased performance demands, the limitations of tenting vias are becoming more evident. Engineers must now evaluate whether traditional Solder Mask Coverage strategies are sufficient—or whether alternative approaches are necessary.

Solder Mask Coverage

1. Understanding Solder Mask Coverage: Definition and Fundamentals

1.1 What is Solder Mask Coverage

Solder Mask Coverage refers to the application of a protective polymer layer—commonly known as solder mask—over selected areas of a PCB surface to:

- Prevent unintended solder bridging

- Protect copper traces from oxidation

- Provide electrical insulation

- Enhance long-term reliability

In the context of vias, Solder Mask Coverage determines whether the via hole is:

- Fully exposed

- Partially covered

- Completely sealed (tented)

Tenting vias specifically means that the solder mask spans across the via opening, forming a thin “tent-like” structure over the hole.

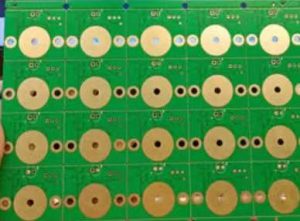

1.2 Types of Solder Mask Coverage for Vias

Different approaches to Solder Mask Coverage include:

| Method | Description | Typical Use Case |

|---|---|---|

| Tented vias | Via covered by solder mask | Low-cost, standard PCBs |

| Plugged vias | Via filled with resin | High-reliability designs |

| Filled & capped vias | Fully filled and plated over | HDI and BGA designs |

| Open vias | No coverage | Test points or thermal vias |

Among these, tenting remains the most widely used due to its simplicity and cost efficiency.

2. Tenting Vias and Solder Mask Coverage: Process Overview

2.1 How Tenting is Achieved in Solder Mask Coverage

The process of tenting involves:

- Applying liquid photoimageable solder mask

- Aligning mask openings with PCB features

- Curing under UV exposure

- Allowing solder mask to span across via holes

Key process factors affecting Solder Mask Coverage include:

- Via diameter

- Solder mask viscosity

- Surface tension

- Lamination pressure

2.2 Critical Design Parameters

For effective tenting:

- Via diameter should typically be ≤ 0.3 mm

- Annular ring must be sufficient

- Mask registration accuracy must be high

Poor control in any of these areas can lead to:

- Mask breakout

- Pinholes

- Incomplete coverage

3. Solder Mask Coverage and Material Science Considerations

3.1 Polymer Chemistry Behind Solder Mask Coverage

At a deeper level, Solder Mask Coverage is not merely a mechanical coating but a chemically engineered polymer system designed to withstand harsh manufacturing and operational environments. Most modern solder masks are based on epoxy-based photoimageable polymers, which combine adhesion strength, chemical resistance, and thermal stability.

These materials are formulated with:

- Epoxy resins for structural integrity

- Photoinitiators for UV curing

- Fillers to control viscosity and mechanical properties

- Pigments (typically green, but also red, black, blue, etc.)

The success of tenting vias depends heavily on how these materials behave during curing. When the solder mask spans across a via hole, it forms a thin membrane. The mechanical strength of this membrane is influenced by:

- Cross-link density after curing

- Thickness uniformity

- Surface adhesion to copper pads

If the polymer network is insufficiently cross-linked, the tent can sag, crack, or rupture during subsequent thermal processes such as reflow soldering.

3.2 Surface Energy and Wetting Behavior in Solder Mask Coverage

Another critical aspect of Solder Mask Coverage is surface energy, which governs how well the liquid solder mask wets the PCB surface and spans across vias.

If the surface energy mismatch is too high:

- The mask may pull away from via edges

- Voids or pinholes may form

- Coverage becomes inconsistent

To mitigate this, PCB manufacturers often perform:

- Plasma cleaning

- Chemical surface treatment

- Micro-etching of copper

These steps improve adhesion and ensure uniform spreading of the solder mask.

In my experience, this is one of the most underestimated contributors to tenting failure. Designers often focus on geometry, but surface preparation quality can make or break the effectiveness of Solder Mask Coverage.

Conclusion

Tenting vias has long been regarded as a practical and economical implementation of Solder Mask Coverage, offering a straightforward way to protect via structures without introducing significant manufacturing complexity. For decades, this method has supported mass production across consumer electronics, industrial controls, and a wide range of standard PCB applications. Its simplicity, compatibility with existing fabrication processes, and low cost have made it a default choice in many designs.

However, as this article has explored in depth, Solder Mask Coverage is no longer a purely protective afterthought—it has become a critical engineering variable that directly influences PCB reliability, electrical performance, thermal behavior, and long-term durability. The evolution of PCB technology toward higher density, smaller geometries, and more demanding operating environments has exposed the inherent limitations of tenting vias. What was once “good enough” in traditional designs may now introduce hidden risks in modern applications.

From a technical perspective, the limitations of tenting stem from both material and structural constraints. The solder mask layer, despite its engineered properties, is still a polymer system subject to thermal expansion, moisture permeability, and mechanical stress. When stretched across via openings, it forms a fragile membrane that can degrade over time due to thermal cycling, environmental exposure, and assembly პროცეს stresses. These vulnerabilities manifest as micro-cracks, mask breakout, delamination, or contamination entrapment—each of which can compromise the integrity of Solder Mask Coverage and, ultimately, the functionality of the PCB.

Equally important is the realization that cost savings achieved through tenting are often short-term. While tented vias reduce initial fabrication costs, they may increase lifecycle costs through reliability issues, field failures, and maintenance requirements. In contrast, more advanced approaches such as via plugging or filling introduce higher upfront expenses but deliver greater consistency and long-term stability. This reinforces a key engineering principle: the most economical solution is not always the least expensive at the point of manufacture.

Another critical takeaway is the importance of context. There is no universal rule that defines the “best” Solder Mask Coverage approach. Instead, the optimal choice depends on a combination of factors, including:

- Application environment (consumer vs industrial vs automotive)

- Electrical performance requirements

- Thermal management needs

- Mechanical stress conditions

- Cost constraints and production volume

In low-risk, cost-sensitive applications, tenting vias remains a valid and efficient solution. However, in high-reliability or high-performance systems—such as HDI boards, high-frequency circuits, or mission-critical electronics—its limitations become too significant to ignore.

This is where collaboration becomes essential. PCB design is no longer an isolated activity; it is a multidisciplinary process that benefits greatly from early and continuous engagement with experienced manufacturing partners. Companies like SQ PCB play a vital role in this ecosystem by helping designers evaluate Solder Mask Coverage options, optimize process parameters, and anticipate potential risks before they materialize. Such collaboration not only improves product quality but also reduces costly iterations and delays.

Looking ahead, the future of Solder Mask Coverage will be shaped by several key trends: material innovation, process automation, and increasing reliance on simulation and predictive modeling. Advances in polymer chemistry may lead to more robust and flexible solder masks, while technologies such as laser direct imaging and AI-driven inspection will enhance precision and consistency. At the same time, the growing complexity of electronic systems will continue to push designers toward hybrid solutions that combine multiple via protection strategies within a single PCB.

In conclusion, tenting vias should not be viewed as an outdated technique, but rather as a situational tool—one that must be applied with a clear understanding of its strengths and limitations. The true challenge for modern engineers is not simply choosing a method of Solder Mask Coverage, but making an informed, strategic decision that balances cost, performance, and reliability across the entire product lifecycle.

Those who approach this decision thoughtfully—grounded in both technical knowledge and practical experience—will be better positioned to design PCBs that meet the demands of today’s technologies while remaining resilient in the face of tomorrow’s challenges.

FAQ

1. Is via filling always better than tenting?

Not necessarily. Via filling offers better reliability but at a higher cost. The choice depends on the specific design requirements.

2. What is Solder Mask Coverage in PCB manufacturing?

It refers to the application of a protective insulating layer over copper traces and vias to prevent oxidation, solder bridging, and electrical faults.

3. Why are tented vias commonly used?

They are cost-effective, simple to manufacture, and suitable for standard PCB designs with low complexity.

4. What are the main disadvantages of tenting vias?

They may suffer from incomplete coverage, reduced thermal performance, and potential reliability issues in harsh environments.

5. When should I avoid using tented vias?

In high-density designs, BGA areas, thermal management regions, and high-reliability applications.

- long board pcb

- Flexible PCBs

- Special PCB

- Express Printed Circuit Board

- Pcb Prototype

- LED PCB

- PCB

- Printed Circuit Board

- Pcb meaning

- Pcb manufacturer

- Rigid pcb board

- Rigid Flex PCB

Quote

Quote

E-mail

E-mail