Enabling Higher Speeds: The Critical Role of Backdrill in Advancing PCB Manufacturing

1: Understanding the Fundamentals — What Backdrill Really Is

1.1 Backdrill Definition and Core Concept (With Backdrill in the Subheading)

Backdrill is a controlled manufacturing process used to remove the unused copper barrel sections—commonly known as stubs—inside plated-through holes (PTH) or vias. These stubs are portions of the via barrel that extend beyond the actual signal layer transition point, and although electrically isolated, they can significantly degrade high-frequency performance.

Key Characteristics of Backdrill

-

Purpose: Eliminate parasitic stub length

-

Method: Mechanical drilling using a bit slightly larger than the via to remove copper plating

-

Goal: Improve high-speed signal transmission by preventing reflection, attenuation, and resonance

-

Typical Usage: Backplanes, server motherboards, data-center switching boards, RF modules, radar PCBs, and 5G network equipment

Why Stubs Must Be Removed

In conventional multilayer PCBs, a through-hole may connect only two or three layers out of ten, twelve, or more. The unused portion behaves like a defective transmission line segment, generating:

-

Signal reflections

-

Undesired resonance

-

Additional insertion loss

-

Phase distortion

These effects become particularly harmful in systems operating above 2–3 GHz, where stub lengths only a few hundred microns can introduce measurable degradation.

Backdrill resolves this issue by physically removing the problematic stub.

1.2 The Physics Behind Backdrill and High-Speed Signals (With Backdrill in the Subheading)

To understand why Backdrill is so effective, we must examine the underlying physics.

Signal Integrity Issues Caused by Stubs

-

Resonant Frequency Distortion

A via stub behaves like an open-circuited transmission line. When its electrical length approaches odd multiples of quarter-wavelength, it creates strong resonances that distort the frequency response. -

Return Loss Deterioration

Reflections increase because the stub provides an impedance discontinuity. As a result, S-parameters (especially S11) worsen. -

Increased Insertion Loss

The unused copper barrel behaves as a load, weakening signal transmission and narrowing usable bandwidth. -

Cross-Talk Enhancement

Stub-related electromagnetic fields expand into adjacent via fields, worsening inter-channel interference. -

Reduced Eye Diagram Opening

Any factor that increases jitter or loss directly reduces system margin.

Impact on 10G/25G/56G/112G Systems

As data rates increase, the tolerance for discontinuities shrinks:

-

10G systems → Backdrill strongly recommended

-

25G systems → Backdrill mandatory

-

56G PAM4 → Nearly impossible to meet specs without Backdrill

-

112G PAM4 → Backdrill plus additional via optimization

This is why many high-speed PCB standards include Backdrill as a required process.

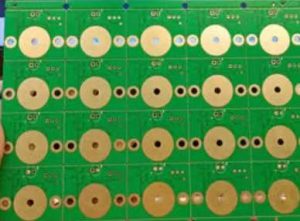

1.3 Manufacturing Process Flow of Backdrill (With Backdrill in the Subheading)

Backdrill occurs after plating but before solder mask application. The general process is:

-

Via Drilling (Primary Drill)

Standard drilling creates PTH vias across the full PCB stack. -

PTH Copper Plating

Electroplating deposits copper inside the via walls. -

Backdrill Layer Mapping

Engineers define the depth to which the drill must remove copper. -

Controlled Backdrilling

A drill bit that is slightly larger than the original via drills from the top or bottom side to the exact depth required. -

Deburring and Cleaning

After drilling, the hole must be cleaned to ensure no debris remains. -

Inspection

-

X-ray

-

Cross-sectioning

-

Laser inspection

-

-

Final Surface Processing

Solder mask application and surface finish occur later.

Backdrill

2: Advantages and Performance Gains from Backdrill

2.1 Backdrill Advantages for Signal Integrity (With Backdrill in the Subheading)

Backdrill offers several key advantages that directly influence design quality:

1. Enhanced High-Speed Signal Integrity

Reducing or eliminating stubs prevents reflections, improving S11 performance.

2. Lower Insertion Loss

Better S21 characteristics lead to:

-

Clearer signal

-

Lower attenuation

-

Wider operational bandwidth

3. Improved Eye Diagrams

By reducing jitter and mode conversion, Backdrill increases both vertical and horizontal eye opening margins.

4. Reduced Electromagnetic Interference (EMI)

Backdrill eliminates resonant structures that radiate RF noise.

5. Better Crosstalk Performance

With less parasitic field coupling, channels behave more independently.

2.2 Backdrill and PCB Performance in High-Speed Applications (With Backdrill in the Subheading)

Backdrill influences the following performance areas:

1. Channel-to-Channel Consistency

Essential for networking equipment, telecom base stations, and optical transceivers.

2. Stable Differential Pair Impedance

Stub elimination ensures balanced propagation.

3. Enhanced Reliability in Harsh Environments

Especially important for aerospace and military products.

4. Improved System Throughput

Because reflections are reduced, transceivers require fewer equalization resources.

5. Compatibility with Advanced Signaling Technologies

Such as:

-

PAM4

-

QAM

-

Ultra-low-jitter clocks

-

SerDes links at 25G/56G/112G

Backdrill is now common in PCB design guidelines for servers, routers, and 5G RU/DU hardware.

2.3 My Reflections on Why Backdrill Has Become a Mainstream Necessity (With Backdrill in the Subheading)

This section expresses my personal technical perspective.

For many years, PCB designers viewed Backdrill as a specialized technique reserved for backplanes or extremely high-speed channels. However, the landscape has changed dramatically:

-

Cloud computing and AI workloads have exploded

-

Data centers rely heavily on 112G links

-

Automotive radar and ADAS require ultra-clean RF pathways

-

5G and upcoming 6G systems push PCBs to new frequency domains

As a result, Backdrill has become a baseline requirement rather than an optional upgrade.

3: Engineering Design Considerations for Backdrill

3.1 Backdrill Layer Mapping and Depth Planning (With Backdrill in the Subheading)

Designing Backdrill requires careful documentation.

Key Parameters

-

Start layer

-

Stop layer

-

Via diameter

-

Backdrill diameter (typically +0.1 mm to +0.15 mm larger)

-

Remaining stub length (target: ≤ 8 mil for 10–25G, ≤ 5 mil for 56G, ≤ 3 mil for 112G)

How Designers Define Depth

Backdrill depth is typically indicated in:

-

Gerber

-

ODB++

-

IPC-2581

-

Mechanical drill tables

The manufacturer then programs CNC machinery with the specified target.

3.2 Stack-Up Design for Backdrill Compatibility (With Backdrill in the Subheading)

The PCB stack-up greatly affects Backdrill feasibility.

Best Practices for Backdrill-Ready Stack-Ups

-

Use consistent dielectric thicknesses near via transitions

-

Avoid placing critical traces near the Backdrill path

-

Keep drill-to-trace clearance > 10 mils (preferably 12–14 mils)

-

Define backdrill for both top and bottom if symmetric

-

Avoid stacking multiple via structures unless necessary

Common Mistakes

-

Backdrill depth not aligned with actual via breakout layers

-

Excessive copper near the drill path causing smear

-

Not coordinating with manufacturer capability

Working with experienced fabricators prevents most of these issues.

3.3 Impact of Backdrill on Mechanical Strength and Reliability (With Backdrill in the Subheading)

Some designers worry that Backdrill may weaken structural integrity. This concern is understandable but often overstated.

Mechanical Considerations

-

Backdrill removes copper, not dielectric; structural weakening is minimal

-

Drilled regions are typically non-load-bearing

-

Manufacturers carefully control drill size to ensure wall stability

When Strength May Be Affected

-

Very small vias (<0.2 mm)

-

High-density via arrays in motorsport or aerospace boards

-

Excessive backdrill depth (operator error)

Mitigation

-

Use reinforced dielectrics

-

Increase pad diameter

-

Use resin-filled microvias instead if structural integrity is critical

With proper design, Backdrill remains extremely reliable.

4: Cost, Manufacturability, and Vendor Capability Analysis

4.1 Cost Drivers of Backdrill Operations in PCB Manufacturing (With Backdrill in the Subheading)

Backdrill brings tremendous electrical advantages, but it is also a non-standard manufacturing step that adds cost. Understanding the primary cost drivers helps designers optimize their stack-ups and minimize unnecessary drilling operations. Backdrill price varies by board thickness, hole count, tool management, and process sequence.

Primary Backdrill Cost Factors

-

Additional CNC drill time

Backdrilling requires a second drilling stage after copper plating. Extra machine cycles increase factory load and cost. -

Tool wear and tool replacement

Backdrill tools wear faster due to copper re-cutting and dielectric abrasion, increasing consumable cost. -

Registration and setup time

Tight mechanical alignment is required to match the original plated-through hole. This adds engineering and calibration workload. -

Depth-specific programming

CNC operators must program layer-specific stopping points. More depth steps = more cost. -

Thicker boards

Thick server backplanes (3.0–8.0 mm) require slow feed rates and longer drilling time. -

High layer counts

More signal layers typically require more Backdrill regions and more complex depth control. -

Small via sizes

Backdrilling small-diameter vias demands high precision, slower speed, and sharper tools.

Cost Reduction Tips for Designers

-

Group critical signals to reduce the number of vias requiring Backdrill.

-

Avoid using Backdrill on low-speed or power nets.

-

Use consistent via sizes to simplify drill programming.

-

Minimize unnecessary layer-transition changes in routing.

-

Collaborate with the manufacturer early to ensure proper design guidance.

Optimized routing and stack-up design may reduce Backdrill cost by up to 30–40%.

4.2 Manufacturability Requirements for Reliable Backdrill Implementation (With Backdrill in the Subheading)

Backdrill adds several manufacturability constraints that designers and fabricators must address early in the design stage.

Key Manufacturability Considerations

-

Minimum Backdrill-to-Copper Clearance

A typical clearance requirement is 8–12 mils (material-dependent). Too little distance increases shorting risk. -

Backdrill Pad Size and Annular Ring Rules

Pads must be large enough to tolerate drill wander and maintain structural integrity. -

Backdrill Region Definition in CAD

Correct layer pairs must be defined in design files; otherwise, fabrication misalignment can occur. -

Avoid High-Density Routing Too Close to Backdrill Holes

Backdrill may create micro-fractures or stress concentrations if copper is too close. -

Consider Material Stack-Up Hardness

Hard materials (e.g., Megtron 7, hydrocarbon ceramics) require slower drill speeds. -

Multilevel Backdrill Complexity

Some boards require Backdrill from both top and bottom, increasing manufacturing complexity.

Fab Notes Designers Should Include

-

Backdrill depth tolerance

-

Drill diameter enlargement rules

-

Clearance requirements

-

Backdrill from top/bottom or both

-

Stub length goals for SI performance

Early communication significantly improves yield.

4.3 Selecting a Backdrill-Capable PCB Vendor (With Backdrill in the Subheading)

Not all PCB manufacturers have the equipment or expertise to perform Backdrill at high precision. Selecting a capable supplier is essential to ensure consistent SI performance and high yield.

Vendor Capability Requirements

-

Dedicated Backdrill CNC Machines

These machines provide closed-loop depth control, high Z-axis accuracy, and real-time drill feedback. -

Experience with High-Speed Boards (10G–224G)

Vendors must understand how Backdrill interacts with differential impedance, crosstalk, and insertion loss. -

Advanced Registration Systems

Necessary to prevent breakout and pad damage. -

X-Ray and AOI Support for Verification

Ensures proper alignment and process consistency. -

Cross-Section Laboratory

A mandatory requirement for Backdrill quality confirmation. -

Thermal Cycling and Reliability Testing

Critical for automotive, 5G, and aerospace projects.

4.4 Balancing Cost, Performance, and Manufacturability in Backdrill Design (With Backdrill in the Subheading)

Designers must strike a balance between cost and performance. Overusing Backdrill increases cost, while underusing it risks signal degradation.

Performance vs. Cost Trade-Off Model

| Priority | Recommended Strategy |

|---|---|

| Maximum performance | Backdrill all high-speed vias (PCIe, SerDes, 5G channels). |

| Balanced design | Backdrill only the most sensitive differential pairs. |

| Cost control | Limit Backdrill to long-stub vias only. |

When Backdrill Helps Most

-

Long-stub plated through holes

-

Non-optimized stack-ups

-

Multi-socket server systems

-

Long interconnect distances

-

Channels above 10G requiring low return loss

When Backdrill Has Marginal Benefit

-

Short traces with minimal vertical transitions

-

Low-speed digital signals

-

Power distribution networks

-

Analog sensor lines

-

IoT and simple consumer electronics

Optimizing Manufacturability

-

Keep via sizes uniform

-

Define Backdrill layers precisely

-

Avoid trace routing near Backdrill regions

-

Maintain reasonable board thickness

-

Confirm rules with the vendor early

This ensures a manufacturable high-speed design without unnecessary cost.

Conclusion

Backdrill has evolved from an optional enhancement into a fundamental requirement for high-speed PCB applications. As data rates climb beyond 10 Gbps, and with 56 Gbps PAM4 and even 112 Gbps channels becoming mainstream, eliminating via stub interference is no longer a luxury—it is a necessity.

This technique provides substantial advantages:

-

Reduced insertion loss

-

Lower reflection and jitter

-

Improved eye-diagram clarity

-

Greater signal-to-noise ratio

-

Enhanced impedance predictability

However, achieving these benefits depends on precise depth control, accurate registration, and disciplined manufacturing processes. Collaborating with experienced fabricators—such as SQ PCB—ensures that engineering intent is fully translated into reliable, high-performance hardware.

Ultimately, Backdrill represents a blend of careful design planning, precise manufacturing technology, and rigorous quality assurance. When executed correctly, it dramatically enhances PCB signal integrity, making it a cornerstone technology for modern high-speed digital systems.

FAQ

1. What is the purpose of Backdrill in PCB manufacturing?

It removes unused via stub sections to reduce signal reflections and improve high-speed transmission quality.

2. How does Backdrill improve signal integrity?

By eliminating stubs, it prevents resonant reflections that would otherwise distort signals, improve insertion loss performance, and reduce jitter.

3. Is Backdrill necessary for all PCBs?

No. It is mainly used for high-speed, high-frequency applications such as servers, routers, 5G equipment, and data-center hardware.

4. Does Backdrill affect the mechanical strength of vias?

Only slightly. When executed correctly within IPC guidelines, structural impact is minimal and within acceptable reliability limits.

5. How deep should a Backdrill operation go?

The drill should stop just above the layer where the signal exits the via, typically leaving less than 10 mil of residual stub.

- long board pcb

- Flexible PCBs

- Special PCB

- Express Printed Circuit Board

- Pcb Prototype

- LED PCB

- PCB

- Printed Circuit Board

- Pcb meaning

- Pcb manufacturer

- Rigid pcb board

- Rigid Flex PCB

Quote

Quote

E-mail

E-mail